Yeah 2 thoughts:

If it works, you can call it the Gepetto fix. Otherwise not

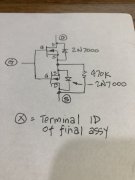

A MOSFET N-Channel enhancement device may also do a much better job than the current N-channel JFET depletion device that is in there now, but that can be reserved for a future discussion.

- The positive bias to the JFET gate is way positive (as in +10V+) during the time you are seeing the 33 and 23 mV and then switches way negative when you see it go back to the level before power on. It could be leakage from the junction FET gate into the drain terminal. This JFET is being biased hard to an on condition during your 8 second period by IC8 (it only takes 0 V at the gate to turn on a JFET, this design is applying ~+10V).

- The ground that the source of each JFET is attached to is really not ground but a ground that is offset by 33 or 23mV from the real ground. This would be a board layout related issue if it is the case. (This is probably unlikely but could exist)

If it works, you can call it the Gepetto fix. Otherwise not

A MOSFET N-Channel enhancement device may also do a much better job than the current N-channel JFET depletion device that is in there now, but that can be reserved for a future discussion.

Last edited: